### Features

- High-performance, Low-power AVR® 8-bit Microcontroller

- Advanced RISC Architecture

- 130 Powerful Instructions Most Single-clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- Nonvolatile Program and Data Memories

- 8K Bytes of In-System Self-Programmable Flash Endurance: 10,000 Write/Erase Cycles

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program True Read-While-Write Operation

- 512 Bytes EEPROM

- Endurance: 100,000 Write/Erase Cycles

- 1K Byte Internal SRAM

- Programming Lock for Software Security

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescaler, one Compare Mode

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Three PWM Channels

- 8-channel ADC in TQFP and MLF package Six Channels 10-bit Accuracy Two Channels 8-bit Accuracy

- 6-channel ADC in PDIP package

Four Channels 10-bit Accuracy

Two Channels 8-bit Accuracy

- Byte-oriented Two-wire Serial Interface

- Programmable Serial USART

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Five Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, and Standby

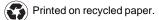

- I/O and Packages

- 23 Programmable I/O Lines

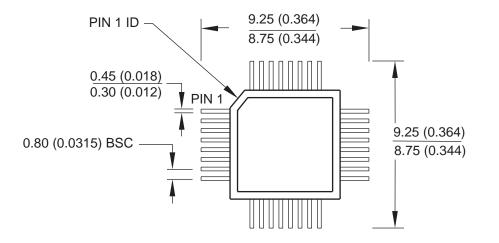

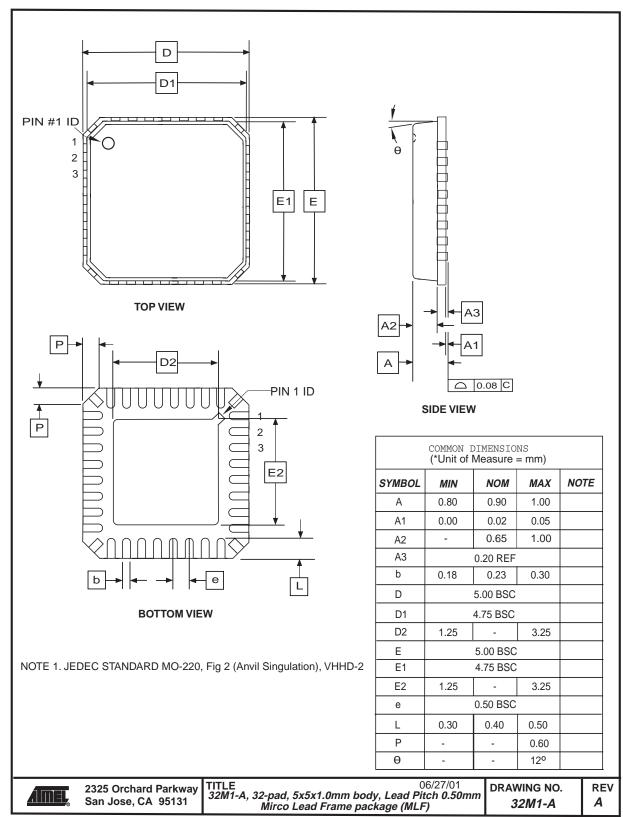

- 28-lead PDIP, 32-lead TQFP, and 32-pad MLF

- Operating Voltages

- 2.7 5.5V (ATmega8L)

- 4.5 5.5V (ATmega8)

- Speed Grades

- 0 8 MHz (ATmega8L)

- 0 16 MHz (ATmega8)

- Power Consumption at 4 Mhz, 3V, 25°C

- Active: 3.6 mA

- Idle Mode: 1.0 mA

- Power-down Mode: 0.5 µA

8-bit **AVR**<sup>®</sup> with 8K Bytes In-System Programmable Flash

# ATmega8 ATmega8L

# Preliminary

# Summary

Note: This is a summary document. A complete document is available on our web site at *www.atmel.com*.

Rev. 2486IS-AVR-12/02

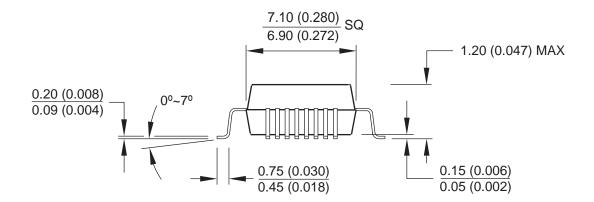

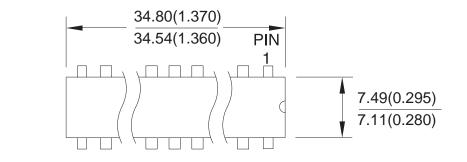

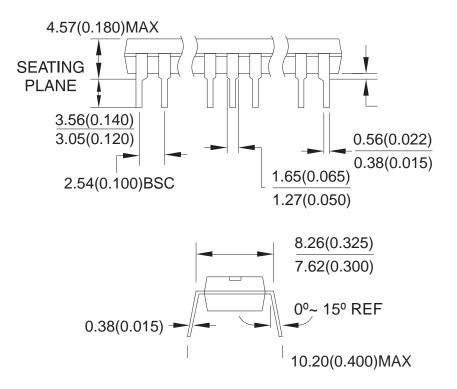

### **Pin Configurations**

<sup>2</sup> ATmega8(L)

#### **Overview**

The ATmega8 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega8 achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed.

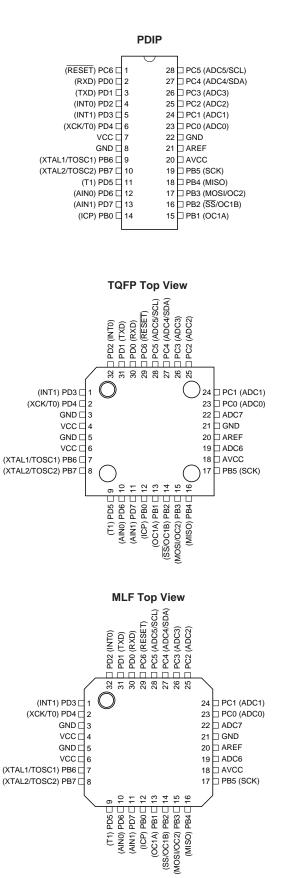

**Block Diagram**

Figure 1. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega8 provides the following features: 8K bytes of In-System Programmable Flash with Read-While-Write capabilities, 512 bytes of EEPROM, 1K byte of SRAM, 23 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, a 6-channel ADC (eight channels in TQFP and MLF packages) where four (six) channels have 10-bit accuracy and two channels have 8-bit accuracy, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and five software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next Interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption.

The device is manufactured using Atmel's high density non-volatile memory technology. The Flash Program memory can be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash Memory. Software in the Boot Flash Section will continue to run while the Application Flash Section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega8 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega8 AVR is supported with a full suite of program and system development tools, including C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

**Disclaimer** Typical values contained in this data sheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

## **Pin Descriptions**

| Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

| Depending on the clock selection fuse settings, PB6 can be used as input to the invert-<br>ing Oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                                                                                                                    |

| Depending on the clock selection fuse settings, PB7 can be used as output from the inverting Oscillator amplifier.                                                                                                                                                                                                                                                                                                                        |

| If the Internal Calibrated RC Oscillator is used as chip clock source, PB76 is used as TOSC21 input for the Asynchronous Timer/Counter2 if the AS2 bit in ASSR is set.                                                                                                                                                                                                                                                                    |

| The various special features of Port B are elaborated on page 56.                                                                                                                                                                                                                                                                                                                                                                         |

| Port C is an 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

| If the RSTDISBL Fuse is programmed, PC6 is used as an I/O pin. Note that the electri-<br>cal characteristics of PC6 differ from those of the other pins of Port C.                                                                                                                                                                                                                                                                        |

| If the RSTDISBL Fuse is unprogrammed, PC6 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 36. Shorter pulses are not guaranteed to generate a Reset.                                                                                                                            |

| The various special features of Port C are elaborated on page 59.                                                                                                                                                                                                                                                                                                                                                                         |

| Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

| Port D also serves the functions of various special features of the ATmega8 as listed on page 61.                                                                                                                                                                                                                                                                                                                                         |

| Reset input. A low level on this pin for longer than the minimum pulse length will gener-<br>ate a reset, even if the clock is not running. The minimum pulse length is given in Table<br>15 on page 36. Shorter pulses are not guaranteed to generate a reset.                                                                                                                                                                           |

| Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                                                                                                                                                                                            |

| Output from the inverting Oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AVCC                                 | AVCC is the supply voltage pin for the A/D Converter, Port C (30), and ADC (76). It should be externally connected to $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to $V_{CC}$ through a low-pass filter. Note that Port C (54) use digital supply voltage, $V_{CC}$ .                                                                                                    |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AREF                                 | AREF is the analog reference pin for the A/D Converter.                                                                                                                                                                                                                                                                                                                                                         |

| ADC76 (TQFP and MLF<br>Package Only) | In the TQFP and MLF package, ADC76 serve as analog inputs to the A/D converter.<br>These pins are powered from the analog supply and serve as 10-bit ADC channels.                                                                                                                                                                                                                                              |

| About Code<br>Examples               | This datasheet contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details. |

## **Register Summary**

| Address                                   | Name          | Bit 7       | Bit 6           | Bit 5           | Bit 4             | Bit 3              | Bit 2           | Bit 1           | Bit 0           | Page             |

|-------------------------------------------|---------------|-------------|-----------------|-----------------|-------------------|--------------------|-----------------|-----------------|-----------------|------------------|

| 0x3F (0x5F)                               | SREG          | I           | т               | н               | S                 | V                  | N               | Z               | с               | 9                |

| 0x3E (0x5E)                               | SPH           | -           | -               | -               | -                 | -                  | SP10            | SP9             | SP8             | 11               |

| 0x3D (0x5D)                               | SPL           | SP7         | SP6             | SP5             | SP4               | SP3                | SP2             | SP1             | SP0             | 11               |

| 0x3C (0x5C)                               | Reserved      |             | 1               | 1               | <b>1</b>          | r                  | <b>1</b>        | 1               | 1               |                  |

| 0x3B (0x5B)                               | GICR          | INT1        | INT0            | -               | -                 | -                  | -               | IVSEL           | IVCE            | 47, 65           |

| 0x3A (0x5A)                               | GIFR          | INTF1       | INTF0           | -               | -                 | -                  | -               | -               | -               | 66               |

| 0x39 (0x59)                               | TIMSK         | OCIE2       | TOIE2           | TICIE1          | OCIE1A            | OCIE1B             | TOIE1           | -               | TOIE0           | 70, 100, 120     |

| 0x38 (0x58)                               | TIFR          | OCF2        | TOV2            | ICF1            | OCF1A             | OCF1B              | TOV1            | -               | TOV0            | 71, 101, 120     |

| 0x37 (0x57)                               | SPMCR         | SPMIE       | RWWSB           | -               | RWWSRE            | BLBSET             | PGWRT           | PGERS           | SPMEN           | 208              |

| 0x36 (0x56)<br>0x35 (0x55)                | TWCR<br>MCUCR | TWINT       | TWEA<br>SM2     | TWSTA<br>SM1    | TWSTO<br>SM0      | TWWC<br>ISC11      | TWEN<br>ISC10   | ISC01           | TWIE<br>ISC00   | 167<br>31, 64    |

| 0x35 (0x55)<br>0x34 (0x54)                | MCUCSR        | -           | -               | -               | -                 | WDRF               | BORF            | EXTRF           | PORF            | 31, 64           |

| 0x33 (0x53)                               | TCCR0         | _           | _               | _               | _                 | -                  | CS02            | CS01            | CS00            | 70               |

| 0x32 (0x52)                               | TCNT0         |             |                 |                 | Timer/Cou         | nter0 (8 Bits)     | 0002            | 0001            | 0000            | 70               |

| 0x31 (0x51)                               | OSCCAL        |             |                 |                 |                   | ibration Register  |                 |                 |                 | 29               |

| 0x30 (0x50)                               | SFIOR         | -           | -               | -               | ADHSM             | ACME               | PUD             | PSR2            | PSR10           | 56, 73, 121, 188 |

| 0x2F (0x4F)                               | TCCR1A        | COM1A1      | COM1A0          | COM1B1          | COM1B0            | FOC1A              | FOC1B           | WGM11           | WGM10           | 95               |

| 0x2E (0x4E)                               | TCCR1B        | ICNC1       | ICES1           | -               | WGM13             | WGM12              | CS12            | CS11            | CS10            | 98               |

| 0x2D (0x4D)                               | TCNT1H        |             |                 | Time            | er/Counter1 – Co  | unter Register Hig | gh Byte         |                 |                 | 99               |

| 0x2C (0x4C)                               | TCNT1L        |             |                 |                 | er/Counter1 – Co  | •                  |                 |                 |                 | 99               |

| 0x2B (0x4B)                               | OCR1AH        |             |                 | Timer/Co        | unter1 – Output C | ompare Register    | A High Byte     |                 |                 | 99               |

| 0x2A (0x4A)                               | OCR1AL        |             |                 |                 | unter1 – Output C |                    |                 |                 |                 | 99               |

| 0x29 (0x49)                               | OCR1BH        |             |                 |                 | unter1 – Output C |                    | · · ·           |                 |                 | 99               |

| 0x28 (0x48)                               | OCR1BL        |             |                 |                 | unter1 – Output C |                    |                 |                 |                 | 99               |

| 0x27 (0x47)                               | ICR1H         |             |                 |                 | Counter1 – Input  |                    |                 |                 |                 | 100              |

| 0x26 (0x46)                               | ICR1L         |             |                 |                 | Counter1 – Input  | · · · · ·          |                 |                 |                 | 100              |

| 0x25 (0x45)                               | TCCR2         | FOC2        | WGM20           | COM21           | COM20             | WGM21              | CS22            | CS21            | CS20            | 115              |

| 0x24 (0x44)                               | TCNT2         |             |                 | т.              |                   | nter2 (8 Bits)     | riotor          |                 |                 | 117              |

| 0x23 (0x43)<br>0x22 (0x42)                | OCR2<br>ASSR  | _           | _               | -               | mer/Counter2 Ou   |                    | TCN2UB          | OCR2UB          | TCR2UB          | 117<br>117       |

| 0x22 (0x42)<br>0x21 (0x41)                | WDTCR         | _           | _               | _               | WDCE              | AS2<br>WDE         | WDP2            | WDP1            | WDP0            | 41               |

|                                           | UBRRH         | URSEL       | _               |                 | -                 | WDL                |                 | R[11:8]         | WDFU            | 154              |

| 0x20 <sup>(1)</sup> (0x40) <sup>(1)</sup> | UCSRC         | URSEL       | UMSEL           | UPM1            | UPM0              | USBS               | UCSZ1           | UCSZ0           | UCPOL           | 152              |

| 0x1F (0x3F)                               | EEARH         | -           | -               | _               | _                 | _                  | _               | _               | EEAR8           | 18               |

| 0x1E (0x3E)                               | EEARL         | EEAR7       | EEAR6           | EEAR5           | EEAR4             | EEAR3              | EEAR2           | EEAR1           | EEAR0           | 18               |

| 0x1D (0x3D)                               | EEDR          |             |                 |                 | EEPROM            | Data Register      |                 |                 |                 | 18               |

| 0x1C (0x3C)                               | EECR          | -           | -               | -               | -                 | EERIE              | EEMWE           | EEWE            | EERE            | 18               |

| 0x1B (0x3B)                               | Reserved      |             |                 |                 |                   |                    |                 |                 |                 |                  |

| 0x1A (0x3A)                               | Reserved      |             |                 |                 |                   |                    |                 |                 |                 |                  |

| 0x19 (0x39)                               | Reserved      |             |                 |                 |                   | 1                  |                 |                 |                 |                  |

| 0x18 (0x38)                               | PORTB         | PORTB7      | PORTB6          | PORTB5          | PORTB4            | PORTB3             | PORTB2          | PORTB1          | PORTB0          | 63               |

| 0x17 (0x37)                               | DDRB          | DDB7        | DDB6            | DDB5            | DDB4              | DDB3               | DDB2            | DDB1            | DDB0            | 63               |

| 0x16 (0x36)                               | PINB          | PINB7       | PINB6           | PINB5           | PINB4             | PINB3              | PINB2           | PINB1           | PINB0           | 63               |

| 0x15 (0x35)                               | PORTC         | -           | PORTC6<br>DDC6  | PORTC5          | PORTC4            | PORTC3             | PORTC2          | PORTC1          | PORTC0          | 63<br>63         |

| 0x14 (0x34)                               | DDRC<br>PINC  | -           | PINC6           | DDC5<br>PINC5   | DDC4<br>PINC4     | DDC3<br>PINC3      | DDC2<br>PINC2   | DDC1<br>PINC1   | DDC0<br>PINC0   | 63               |

| 0x13 (0x33)<br>0x12 (0x32)                | PINC          | –<br>PORTD7 | PINC6<br>PORTD6 | PINC5<br>PORTD5 | PINC4<br>PORTD4   | PINC3<br>PORTD3    | PINC2<br>PORTD2 | PINC1<br>PORTD1 | PINC0<br>PORTD0 | 63               |

| 0x12 (0x32)<br>0x11 (0x31)                | DDRD          | DDD7        | DDD6            | DDD5            | DDD4              | DDD3               | DDD2            | DDD1            | DDD0            | 63               |

| 0x10 (0x30)                               | PIND          | PIND7       | PIND6           | PIND5           | PIND4             | PIND3              | PIND2           | PIND1           | PIND0           | 63               |

| 0x0F (0x2F)                               | SPDR          |             |                 |                 |                   | ta Register        |                 |                 |                 | 128              |

| 0x0E (0x2E)                               | SPSR          | SPIF        | WCOL            | -               | -                 | _                  | -               | -               | SPI2X           | 128              |

| 0x0D (0x2D)                               | SPCR          | SPIE        | SPE             | DORD            | MSTR              | CPOL               | СРНА            | SPR1            | SPR0            | 126              |

| 0x0C (0x2C)                               | UDR           |             | •               | •               |                   | Data Register      | ·               | •               | ·               | 149              |

| 0x0B (0x2B)                               | UCSRA         | RXC         | TXC             | UDRE            | FE                | DOR                | PE              | U2X             | MPCM            | 150              |

| 0x0A (0x2A)                               | UCSRB         | RXCIE       | TXCIE           | UDRIE           | RXEN              | TXEN               | UCSZ2           | RXB8            | TXB8            | 151              |

| 0x09 (0x29)                               | UBRRL         |             |                 |                 | USART Baud Ra     | te Register Low E  | Byte            |                 |                 | 154              |

| 0x08 (0x28)                               | ACSR          | ACD         | ACBG            | ACO             | ACI               | ACIE               | ACIC            | ACIS1           | ACIS0           | 189              |

| 0x07 (0x27)                               | ADMUX         | REFS1       | REFS0           | ADLAR           | -                 | MUX3               | MUX2            | MUX1            | MUX0            | 200              |

| 0x06 (0x26)                               | ADCSRA        | ADEN        | ADSC            | ADFR            | ADIF              | ADIE               | ADPS2           | ADPS1           | ADPS0           | 202              |

| 0x05 (0x25)                               | ADCH          |             |                 |                 |                   | gister High Byte   |                 |                 |                 | 203              |

| 0x04 (0x24)                               | ADCL          |             |                 |                 |                   | egister Low Byte   |                 |                 |                 | 203              |

| 0x03 (0x23)                               | TWDR          |             |                 | 1               | wo-wire Serial In |                    |                 |                 |                 | 169<br>169       |

|                                           |               | TWA6        | TWA5            | T<br>TWA4       |                   | * ·                | ister<br>TWA1   | TWA0            | TWGCE           |                  |

### **Register Summary (Continued)**

| Address     | Name | Bit 7 | Bit 6                                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Page |

|-------------|------|-------|---------------------------------------------|-------|-------|-------|-------|-------|-------|------|

| 0x01 (0x21) | TWSR | TWS7  | TWS6                                        | TWS5  | TWS4  | TWS3  | -     | TWPS1 | TWPS0 | 168  |

| 0x00 (0x20) | TWBR |       | Two-wire Serial Interface Bit Rate Register |       |       |       |       |       |       | 167  |

Notes: 1. Refer to the USART description for details on how to access UBRRH and UCSRC.

2. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

3. Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

## Instruction Set Summary

| ARITHMETIC AND L                                                                                                     | Operands                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                           | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Flags                                                                                                                                                                                                                                                                                                                                                  | #Clocks                                                            |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|                                                                                                                      | OGIC INSTRUCTIONS                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                        | -                                                                  |

| ADD                                                                                                                  | Rd, Rr                                                                               | Add two Registers                                                                                                                                                                                                                                                                                                                                                                     | $Rd \leftarrow Rd + Rr$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Z,C,N,V,H                                                                                                                                                                                                                                                                                                                                              | 1                                                                  |

| ADC                                                                                                                  | Rd, Rr                                                                               | Add with Carry two Registers                                                                                                                                                                                                                                                                                                                                                          | $Rd \gets Rd + Rr + C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Z,C,N,V,H                                                                                                                                                                                                                                                                                                                                              | 1                                                                  |

| ADIW                                                                                                                 | Rdl,K                                                                                | Add Immediate to Word                                                                                                                                                                                                                                                                                                                                                                 | $Rdh:\!Rdl \gets Rdh:\!RdI + K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Z,C,N,V,S                                                                                                                                                                                                                                                                                                                                              | 2                                                                  |

| SUB                                                                                                                  | Rd, Rr                                                                               | Subtract two Registers                                                                                                                                                                                                                                                                                                                                                                | $Rd \leftarrow Rd - Rr$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Z,C,N,V,H                                                                                                                                                                                                                                                                                                                                              | 1                                                                  |

| SUBI                                                                                                                 | Rd, K                                                                                | Subtract Constant from Register                                                                                                                                                                                                                                                                                                                                                       | $Rd \gets Rd - K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Z,C,N,V,H                                                                                                                                                                                                                                                                                                                                              | 1                                                                  |

| SBC                                                                                                                  | Rd, Rr                                                                               | Subtract with Carry two Registers                                                                                                                                                                                                                                                                                                                                                     | $Rd \gets Rd - Rr - C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Z,C,N,V,H                                                                                                                                                                                                                                                                                                                                              | 1                                                                  |

| SBCI                                                                                                                 | Rd, K                                                                                | Subtract with Carry Constant from Reg.                                                                                                                                                                                                                                                                                                                                                | $Rd \gets Rd - K - C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Z,C,N,V,H                                                                                                                                                                                                                                                                                                                                              | 1                                                                  |

| SBIW                                                                                                                 | Rdl,K                                                                                | Subtract Immediate from Word                                                                                                                                                                                                                                                                                                                                                          | Rdh:Rdl ← Rdh:Rdl - K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Z,C,N,V,S                                                                                                                                                                                                                                                                                                                                              | 2                                                                  |

| AND                                                                                                                  | Rd, Rr                                                                               | Logical AND Registers                                                                                                                                                                                                                                                                                                                                                                 | $Rd \leftarrow Rd \bullet Rr$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Z,N,V                                                                                                                                                                                                                                                                                                                                                  | 1                                                                  |

| ANDI                                                                                                                 | Rd, K                                                                                | Logical AND Register and Constant                                                                                                                                                                                                                                                                                                                                                     | $Rd \gets Rd \bullet K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Z,N,V                                                                                                                                                                                                                                                                                                                                                  | 1                                                                  |

| OR                                                                                                                   | Rd, Rr                                                                               | Logical OR Registers                                                                                                                                                                                                                                                                                                                                                                  | $Rd \leftarrow Rd \lor Rr$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Z,N,V                                                                                                                                                                                                                                                                                                                                                  | 1                                                                  |

| ORI                                                                                                                  | Rd, K                                                                                | Logical OR Register and Constant                                                                                                                                                                                                                                                                                                                                                      | $Rd \leftarrow Rd \lor K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Z,N,V                                                                                                                                                                                                                                                                                                                                                  | 1                                                                  |

| EOR                                                                                                                  | Rd, Rr                                                                               | Exclusive OR Registers                                                                                                                                                                                                                                                                                                                                                                | $Rd \leftarrow Rd \oplus Rr$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Z,N,V                                                                                                                                                                                                                                                                                                                                                  | 1                                                                  |

| COM                                                                                                                  | Rd                                                                                   | One's Complement                                                                                                                                                                                                                                                                                                                                                                      | $Rd \leftarrow 0xFF - Rd$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Z,C,N,V                                                                                                                                                                                                                                                                                                                                                | 1                                                                  |

| NEG                                                                                                                  | Rd                                                                                   | Two's Complement                                                                                                                                                                                                                                                                                                                                                                      | Rd ← 0x00 - Rd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Z,C,N,V,H                                                                                                                                                                                                                                                                                                                                              | 1                                                                  |

| SBR                                                                                                                  | Rd,K                                                                                 | Set Bit(s) in Register                                                                                                                                                                                                                                                                                                                                                                | $Rd \leftarrow Rd \vee K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Z,N,V                                                                                                                                                                                                                                                                                                                                                  | 1                                                                  |

| CBR                                                                                                                  | Rd,K                                                                                 | Clear Bit(s) in Register                                                                                                                                                                                                                                                                                                                                                              | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Z,N,V                                                                                                                                                                                                                                                                                                                                                  | 1                                                                  |

| INC                                                                                                                  | Rd                                                                                   | Increment                                                                                                                                                                                                                                                                                                                                                                             | $Rd \leftarrow Rd + 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Z,N,V<br>Z,N,V                                                                                                                                                                                                                                                                                                                                         | 1                                                                  |